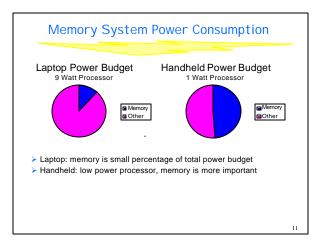

## Memory: The Unturned Stone

- Previous Architecture/OS Energy Studies:

- > Disk spindown policies [Douglis, Krishnan, Helmbold, Li]

- Processor voltage and clock scaling [Weiser, Pering, Lorch, Farkas et al]

- Network Interface [Stemm, Kravets]

- > Mems-based storage [Nagle et al]

- Application-aware adaptation & API [Flinn&Satya]

- > But where is main memory management?

Power Aware Page Allocation [ASPLOS00]

10

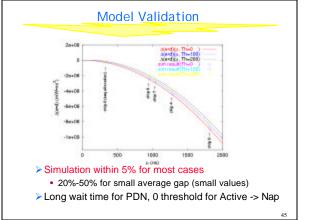

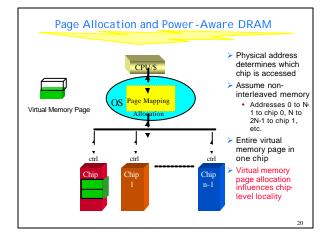

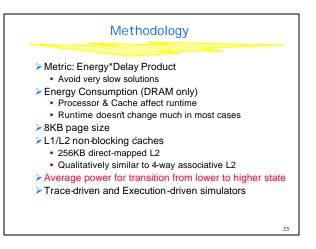

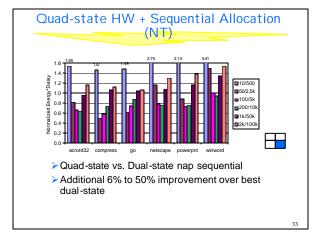

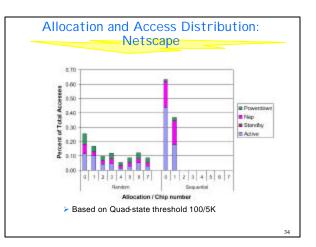

## Methodology Continued

- Trace-Driven Simulation

- Windows NT personal productivity applications (Etch at Washington)

- Simplified processor and memory model

- Eight outstanding cache misses

- Eight 32Mb chips, total 32MB, non-interleaved

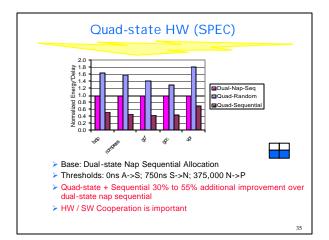

- Execution-Driven Simulation

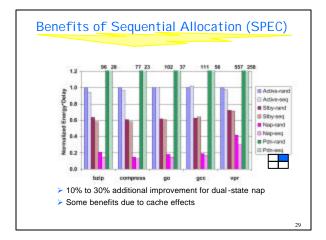

- SPEC benchmarks (subset of integer)

- SimpleScalar w/ detailed RDRAM timing and power models

- Sixteen outstanding cache misses

- Eight 256Mb chips, total 256MB, non-interleaved

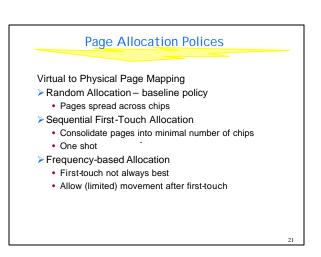

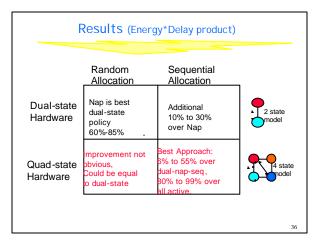

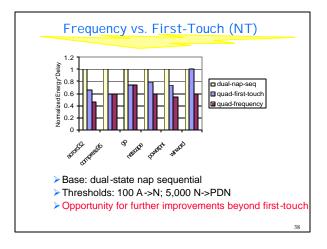

## Better Page Allocation Policies?

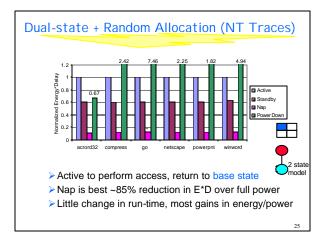

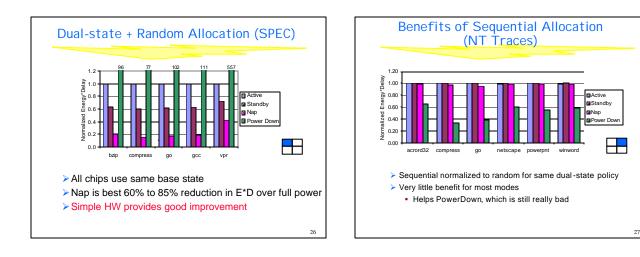

- Intuitively, first-touch will not always be best

- > Allow movement after first-touch as "corrections"

- Frequency-based allocation

- Preliminary results

- Offline algorithm: sort by page count

- Allocate sequentially in decreasing order

- Packs most frequently accessed pages into first chip

Provides insight into potential benefits (if any) of page movement and motivate an on-line algorithm

> Data collection hardware

- Reserve n pages in chip 0 (n=128)

- 10-bit saturating counter per physical page

- On-line Algorithm

- Warmup for 100ms, sample accesses for 2ms

- Sort counts, move 128 most frequent pages to reserved pages in hot chip, repack others into minimum number of chips

- Preliminary experiments and results

Use 0.011ms and 0.008mJ for page move

- Ose 0.01 ms and 0.000ms for page in

10% improvement for winword

- Need to consider in execution-driven simulator

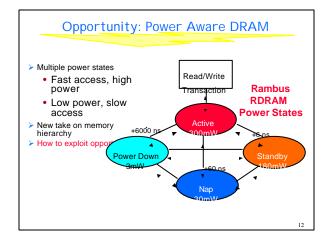

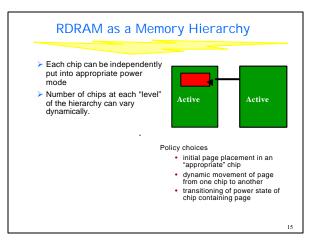

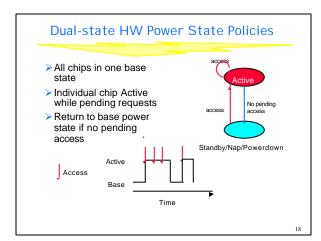

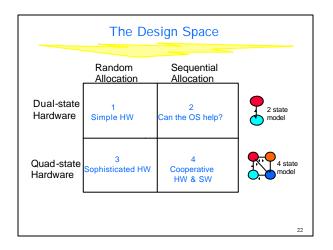

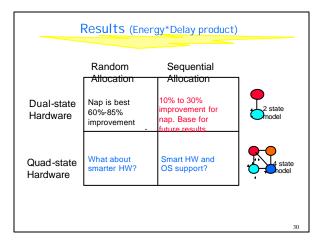

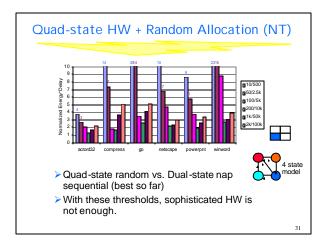

- Hardware Policies

- Without OS support

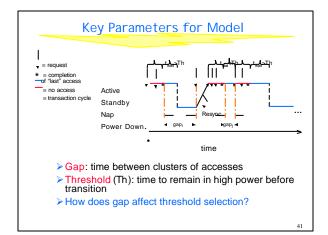

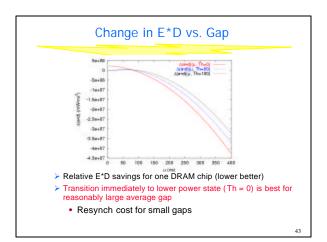

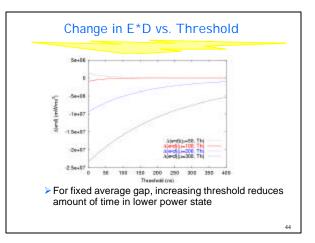

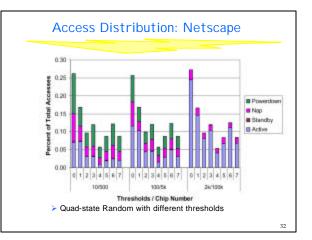

Thresholds not obvious

- With OS support

- Idle DRAM chips power down

- Can we decouple thresholds for Nap & Power down?

- Recent studies advocate "smarter" polices [Delaluz HPCA '01]

No caches, no virtual memory

- > Are "smarter" policies required for cache-based systems?

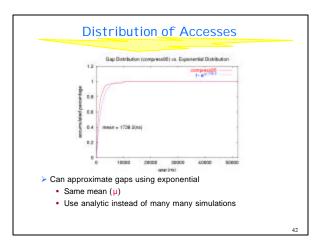

- Use analytic modeling to evaluate space

- > Validate with simulation